在模拟CMOS集成电路设计中,MOS管的性能参数与外围电路设计至关重要。其中,RC吸收电路的计算和MOS管的截止频率(ft)是影响电路高频响应、稳定性和效率的核心因素。本文将系统探讨这三个关键主题。

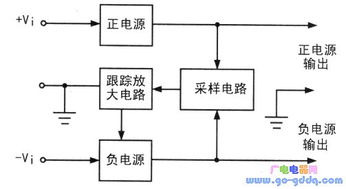

一、MOS管RC吸收电路的计算

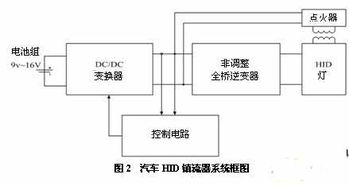

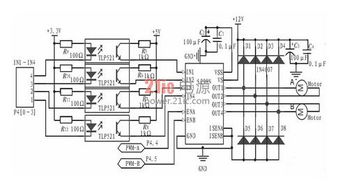

RC吸收电路(也称为缓冲电路或阻尼电路)常用于开关电源、功率驱动等电路中,其目的是抑制由MOS管快速开关引起的电压尖峰和振铃现象,这些现象源于线路中的寄生电感和电容。

1. 电路作用与原理

RC吸收电路通常并联在MOS管的漏极和源极之间(对于电压尖峰)或栅极电阻上(对于栅极振铃)。其基本原理是利用电阻R消耗振铃能量,同时利用电容C限制电压变化率(dv/dt)。

2. 关键参数计算

计算RC值通常基于对振铃频率的抑制。首先需要估算寄生参数:

- 寄生电感(Lp):主要由引线和PCB走线产生,可通过测量或仿真估算。

- 寄生电容(Cp):主要包括MOS管的输出电容(Coss)和布线电容。

振铃的固有频率fring约为:f</em>ring ≈ 1 / (2π√(Lp * Cp))

为了有效阻尼振铃,RC吸收电路的转折频率应设定在振铃频率附近。一个常用的经验公式是:R ≈ √(Lp / Cp)C ≥ (1 / (2π <em> f_ring </em> R)) 且通常选择C值比Cp大数倍(例如2-10倍),以确保有足够的吸收效果,但过大的C会增加开关损耗。

3. 设计权衡

- 电阻R:R值太小会增大开关损耗,太大则阻尼效果不足。

- 电容C:C值越大,吸收效果越好,但会降低开关速度并增加损耗。

实际设计中常通过实验或仿真(如SPICE)进行微调,以达到最佳的效率与EMI平衡。

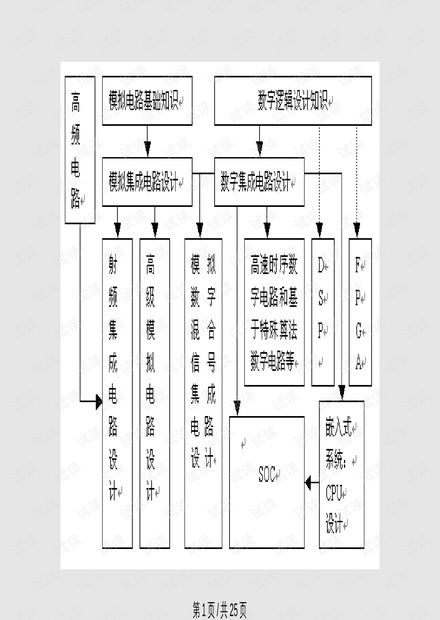

二、模拟CMOS集成电路设计中的考量

在模拟CMOS IC设计中,MOS管是构建放大器、比较器、电流源等基本模块的核心。设计与优化围绕几个关键方面:

1. 工作区域

- 饱和区:用于放大和恒流源,要求Vds > Vgs - Vth(过驱动电压)。

- 线性/三极管区:用作可控电阻,如开关或模拟开关。

2. 关键设计参数

- 宽长比(W/L):决定跨导(gm)、电流驱动能力和寄生电容。

- 过驱动电压(Vov = Vgs - Vth):影响增益、带宽和噪声性能。

- 本征增益(gm/gds):在深亚微米工艺中下降,是放大器设计的重要限制。

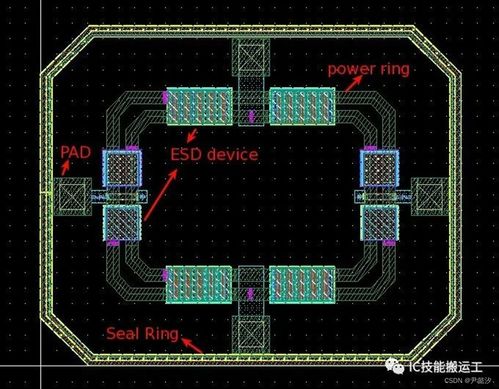

3. 匹配与布局

模拟设计极度重视器件匹配。采用共质心、叉指等布局技术,并遵守设计规则,以减小工艺偏差对差分对、电流镜等电路性能的影响。

三、MOS管的截止频率(ft)

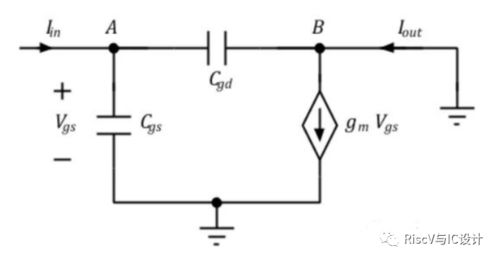

截止频率ft是衡量MOS管高频性能的核心指标,定义为当小信号电流增益下降到1(0 dB)时的频率。

1. 定义与公式

ft反映了器件本身的速度极限。对于工作在饱和区的长沟道MOS管,其近似公式为:ft ≈ gm / (2π * Cgs)

其中:

gm是跨导,与偏置电流和W/L相关。Cgs是栅源电容,是限制高频响应的主要电容。

对于短沟道器件,公式需修正,但gm/Cgs的比例关系仍是关键。

2. 物理意义与影响因素

- ft越高,意味着器件能有效工作的频率越高。

- 提升ft的途径:

a. 增大gm:通过增大W/L或提高偏置电流(但会增加功耗)。

b. 减小Cgs:使用更小尺寸的器件(按比例缩小),但会受短沟道效应限制。

- 在实际电路中,ft只是一个理想值。电路的实际工作频率(如放大器的增益带宽积GBW)远低于ft,因为还要考虑负载电容、密勒效应(如Cgd)以及互连线寄生参数。

3. 在IC设计中的应用

设计高速电路(如RF前端、高速SerDes)时,必须选择ft远高于目标工作频率的器件。需要精心设计版图以最小化寄生电容和电阻,使电路性能接近器件的ft极限。

###

在模拟CMOS集成电路设计中,MOS管RC吸收电路的计算是保障电路可靠性的实用技能,其核心在于根据寄生参数合理选择R和C以阻尼振铃。而电路设计的本质,则是基于对MOS管工作区域、跨导、增益等参数的深刻理解。MOS管的截止频率ft则从器件物理层面定义了其频率能力的上限,是评估和选择工艺、指导高速电路设计的基础指标。三者相辅相成,共同构成了高性能、高可靠性模拟IC设计的基石。在实际工程中,理论计算、仿真验证与实验测试必须紧密结合,才能实现最优设计。