在集成电路(IC)产业蓬勃发展的今天,电子设计自动化(EDA)工具作为连接芯片设计与制造的“灵魂”与“桥梁”,其战略地位不言而喻。长期以来,全球EDA市场被少数几家国际巨头所垄断,国产EDA软件则长期在关键技术与市场认可的双重“夹缝”中艰难求索。本文将聚焦于国产EDA在集成电路从设计到制造的全流程中所面临的挑战与机遇。

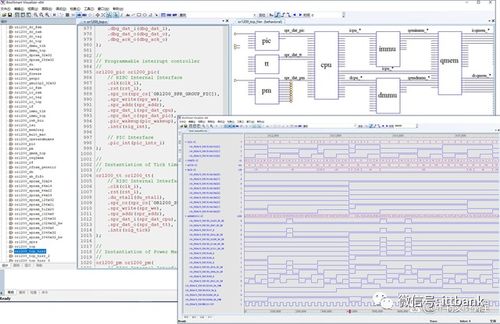

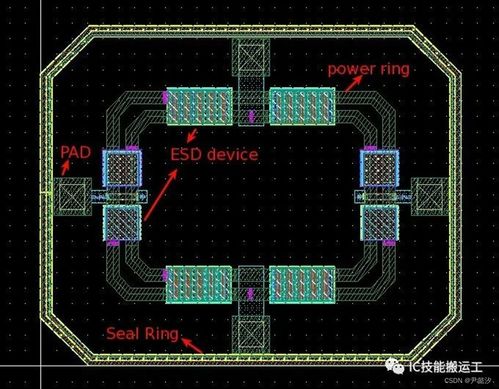

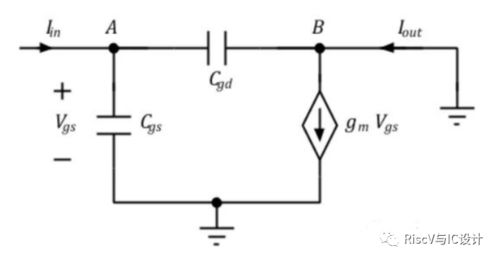

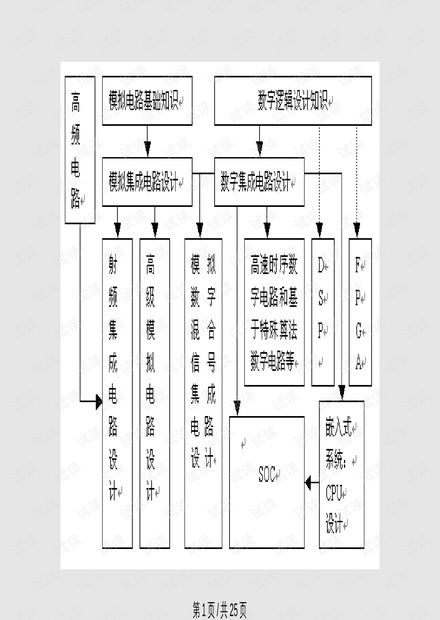

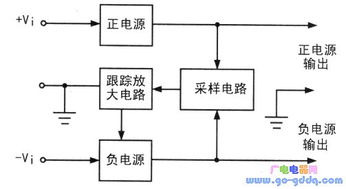

集成电路的诞生是一个复杂而精密的过程,大体可分为设计与制造两大核心环节。在设计端,工程师利用EDA工具完成从系统架构、逻辑设计、电路仿真到物理版图(Layout)生成等一系列工作。这要求EDA软件具备强大的算法支撑,能够处理数以亿计的晶体管连接,并确保设计的正确性、性能和功耗达标。在制造端,芯片设计好的版图数据(GDSII文件)被送往晶圆厂,经过光刻、刻蚀、离子注入等数百道工序,最终在硅片上实现三维结构的雕刻。而制造工艺的复杂性(如纳米级制程、多重曝光技术)又对设计端提出了严苛的工艺规则检查(DRC)、版图与电路图一致性检查(LVS)等要求,这同样依赖于高度专业化的制造类EDA工具。

正是在这个环环相扣的流程中,国产EDA的“夹缝”困境清晰可见。

是 “技术生态夹缝”。国际主流EDA工具经过数十年发展,已与全球领先的晶圆厂(如台积电、三星)的先进工艺节点深度捆绑,形成了“工艺文件-PDK(工艺设计套件)-EDA工具”的紧密闭环。国产EDA企业若想进入高端设计市场,必须获得这些晶圆厂的工艺支持和认证,这本身就是一个极高的门槛。国际EDA巨头通过提供覆盖全流程的完整工具链,建立了强大的用户黏性和设计习惯,国产工具往往只能在局部点工具上实现突破,难以融入既有的、以国外工具为主的设计流程。

是 “市场信任夹缝”。芯片设计投入动辄数亿,流片成本极高,任何设计工具的不稳定都可能带来灾难性后果。因此,设计公司,尤其是大型企业,对采用新EDA工具极为谨慎。国产EDA在成熟度和可靠性上与国际领先产品仍有差距,导致其难以进入核心设计环节,多用于教学、部分模拟芯片或特定验证场景。缺乏高端市场的大规模应用反馈,又进一步制约了其技术迭代的速度,形成某种循环。

是 “人才与资本夹缝”。EDA是算法密集、工程实践要求极高的领域,需要兼备数学、计算机和微电子知识的复合型顶尖人才。国内相关人才本就稀缺,且多数被国际EDA公司在华机构或国内互联网巨头吸纳。EDA研发投入大、周期长、见效慢,在资本追求快速回报的环境下,国产EDA企业长期面临融资和发展压力。

夹缝之中,亦见曙光。全球半导体产业格局动荡与供应链安全焦虑,为国产EDA提供了前所未有的战略机遇。国家政策大力扶持,资本市场关注度提升,一批国产EDA企业开始在特定领域崭露头角:

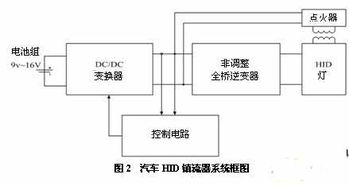

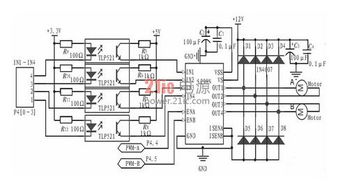

- 聚焦细分,单点突破:在模拟电路设计、物理验证、封装测试、半导体器件建模等环节,部分国产工具已达到或接近国际水平,实现了进口替代。

- 拥抱新赛道,换道超车:在先进封装(如Chiplet)、人工智能芯片设计、开源EDA等新兴领域,国内外起步差距相对较小,国产EDA有望构建新的生态。

- 产业链协同,合力突围:国内晶圆制造产能(如中芯国际、华虹)的持续提升,为国产EDA提供了宝贵的工艺适配和联合研发机会。国内芯片设计公司的崛起,也产生了对自主可控工具链的真实需求。

国产EDA的生存与发展,绝非一朝一夕之功。它需要持续的战略定力、长期的研发投入、开放的产业合作以及耐心的人才培养。路径或许清晰:先从能够嵌入现有流程的可靠点工具做起,逐步向特定领域全流程解决方案拓展,最终通过与国内制造、设计环节的深度协同,构建起自主可控的集成电路产业生态基石。这条路充满挑战,但在大国竞争与科技自立的时代背景下,打破EDA的“夹缝”生存状态,已不仅是商业命题,更是关乎中国集成电路产业长远发展的关键一役。