在科技飞速发展的今天,从我们手中的智能手机,到正在改变未来的自动驾驶汽车和人工智能,其核心驱动力往往源于一枚枚比指甲盖还小的硅片——集成电路。这些功能强大的“大脑”并非天成,其背后是精密、复杂且充满挑战的集成电路设计过程。让我们一同走进这个微观世界的宏观创造,聊聊集成电路设计的那些事儿。

集成电路设计,俗称“芯片设计”,是一个将系统、逻辑与性能要求转化为具体物理版图的创造性过程。它始于一个抽象的概念或功能需求,终于一张能被晶圆厂精确制造出来的设计图纸。整个过程犹如在纳米尺度上建造一座功能齐全的超级城市,需要规划“街区”(功能模块)、铺设“道路”(互连线)、确保“水电供应”(电源与时钟网络),并保证“交通”顺畅无阻。

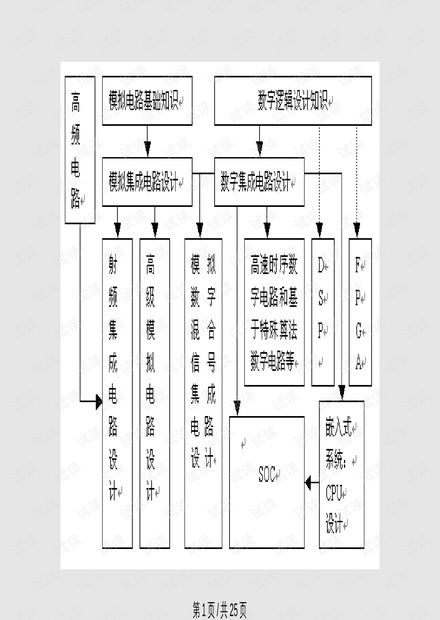

这个宏大的工程通常遵循一个分层设计的流程。

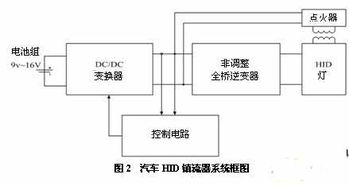

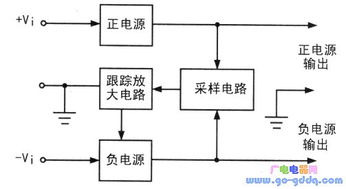

是系统架构设计。这好比是城市的总体规划师,需要确定芯片的核心目标、整体架构、关键模块(如CPU核心、GPU、内存控制器等)以及它们之间的交互方式。性能、功耗、成本是这一阶段需要反复权衡的“铁三角”。

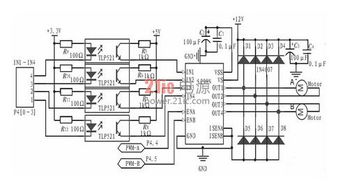

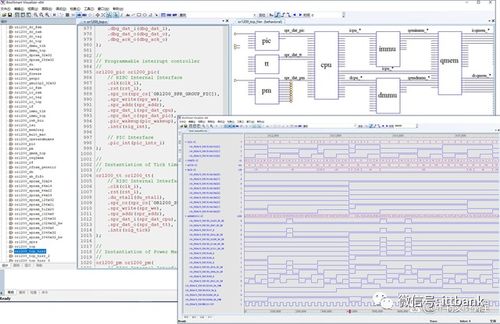

接着,进入前端设计。设计师们使用硬件描述语言(如Verilog或VHDL),像编写高级程序一样,将架构转化为可综合的寄存器传输级代码。这个过程定义了芯片的逻辑功能。通过功能仿真、逻辑综合等工具,将代码转换成由基本逻辑门(与、或、非门等)和触发器组成的网表,并进行严格的验证,确保逻辑功能万无一失。

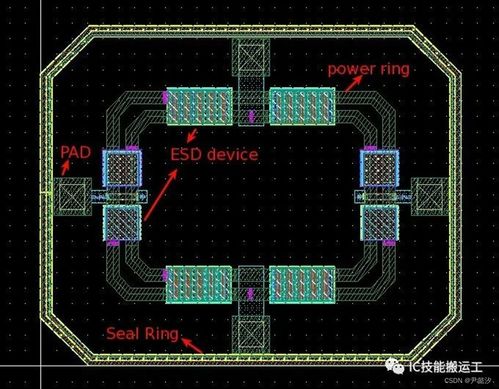

然后,是更为精细复杂的后端设计,也称为物理设计。这是将逻辑网表“安家落户”到实际硅片上的过程。主要步骤包括:

- 布局:将成千上万个逻辑单元在芯片平面上合理地摆放好,就像规划城市中建筑的位置。

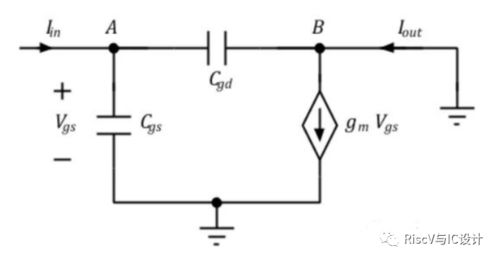

- 布线:用金属导线将这些单元按照逻辑关系连接起来,形成纵横交错的“交通网”。在纳米工艺下,布线需要考虑信号完整性、串扰、延迟等诸多物理效应。

- 时序收敛与物理验证:确保所有信号能在要求的时间内到达,并满足制造工艺的所有物理规则(如线宽、间距)。这个过程往往需要多次迭代,是设计中最耗时、最考验工程师经验的环节之一。

设计完成后,生成的最终版图文件(GDSII)将被送往晶圆厂进行流片制造。一颗芯片的设计周期漫长,投入巨大,动辄数千万美元。因此,设计过程中的任何微小失误都可能导致“流片失败”,造成巨额损失,这使得验证工作至关重要。

当今的集成电路设计也面临着巨大挑战与革新。随着工艺节点进入5纳米、3纳米甚至更小,晶体管尺寸逼近物理极限,量子隧穿等效应日益显著,功耗和散热问题空前严峻。这推动了设计方法的变革:从单纯追求性能的“更高、更快、更强”,转向以“能效比”为核心的系统级优化。异质集成、芯粒技术、硅光互联等新范式正在兴起。人工智能也开始赋能设计流程,用于加速布局布线、优化功耗,甚至辅助架构探索。

总而言之,集成电路设计是一门融合了电子工程、计算机科学、物理学和数学的尖端学科。它既需要工程师具备严谨的逻辑思维和深厚的理论功底,又要求他们拥有天马行空的创造力和解决复杂问题的韧性。每一枚成功面世的芯片,都是无数工程师智慧和心血的结晶,是推动人类社会向智能时代迈进的核心基石。那些发生在EDA工具里、仿真服务器上、以及工程师们头脑风暴中的“设计那些事儿”,正悄然塑造着我们未来的模样。